众所周知,全球首款3nm手机芯片A17 Pro也随着iPhone15的到来与大家见面了。

虽然这款芯片发布后,大家都抱怨CPU和GPU提升太少,只有NPU有明显提升。但不可否认的是,相比安卓芯片,苹果的A17芯片已经足够先进,至少领先安卓芯片2代。

如果不出意外的话,高通和联发科很快就会推出3nm手机芯片,然后三星也可以跟进推出3nm手机芯片。

那么很多人会问如何判断一个芯片是否是3nm? 3nm代表着芯片中哪些重要参数?或者我们谈论的是3nm芯片,只是晶圆厂随口说的?如果他们说 3nm,那就是 3nm,如果他们说 5nm,那就是 5nm?

其实你是对的。目前3nm芯片的关键参数都不是3nm的。现在的3nm、5nm确实是营销手段。华夫饼工厂拥有最终决定权。

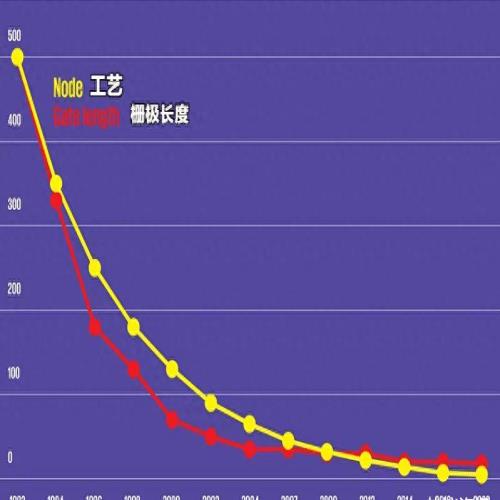

事实上,在130nm之前,芯片的纳米数是指金属半节距(metal half-pitch)的纳米数或栅极长度(gate length)的纳米数。

随着每一代工艺的进步,栅极长度和金属半高通常会减少 30%,晶体管密度加倍,面积减半。

但后来晶圆厂盲目缩短栅极长度,导致130nm时实际栅极长度仅为70nm。这个过程与栅极长度脱节。

后来,栅极长度落后于工艺,因为随着工艺的不断发展,栅极长度无法继续每代缩小30%。

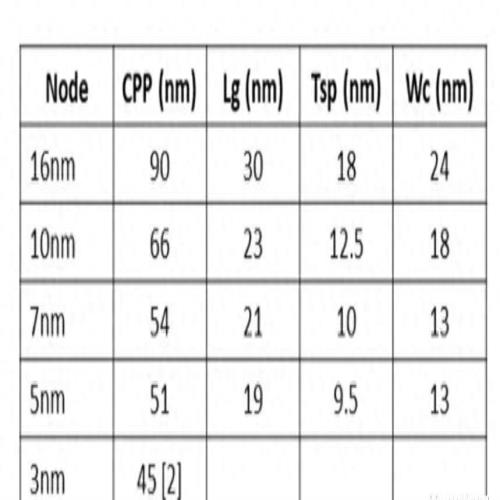

后来,科学家们引入了一种新的术语,称为接触栅间距,它指的是一个晶体管的栅极与另一个晶体管的栅极之间的最小距离。一半距离代表芯片工艺。

但这种命名方式损害了晶圆厂的利益,因为减少接触口间距太难了,所以后来晶圆厂不再关心栅极长度、金属半、接触口间距等。

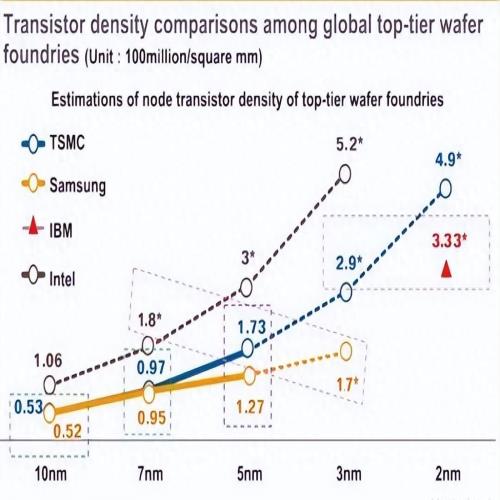

直接遵循您自己的进度并命名您自己的流程。所以我们看到进入10nm之后,几个厂商的工艺当然是不一样的,每个人的晶体管密度也完全不一样。

台积电和三星的7nm与英特尔的10nm持平。台积电的5nm相当于三星的3nm、英特尔的7nm。

可见,各个晶圆厂对多少纳米工艺的定义是不同的。如果大家的定义都一样,那么理论上晶体管密度应该是一样的。不过,我们仍然可以将其应用到台积电的芯片上,接触端口之间距离的一半处,看看实际使用了多少纳米工艺。

据媒体爆料,台积电7nm工艺的接触式多晶硅间距(CPP)为54nm,这意味着实际工艺应该在27nm左右。

5nm时,CPP值为51nm,实际应该在25nm左右。 3nm时,CPP值为45nm,实际应该是22nm。

以上说法仅供参考。毕竟没有人用一半的接触栅间距来命名芯片工艺,所以这是见仁见智的问题。

但大家还是要明白一个道理,那就是现在的纳米数确实是晶圆厂自己命名的。想怎么称呼也是晶圆厂自己的权利。

免责声明:发表本文是为了传达更多信息。若来源侵犯您的合法权益,请联系我们删除。