本文内容非商业用途可无需授权转载,请务必注明作者、微博ID:唐僧_huangliang,以便更好地与读者互动。

今天去参加了一个存储方面的会议,但没啥太多心得,索性写点服务器的东西。

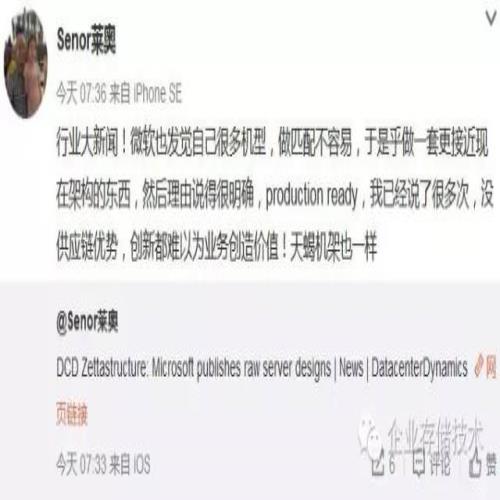

昨天看到国外一条新闻,微软开放了一款完成一半的Azure服务器,贡献给由Facebook发起的OCP组织。下面是我在微博上看到两位业内专家的观点:

在最近一次的ODCC(开放数据中心委员会)2016峰会上,也强调过组件的规范化,以便不同供应商之间能够在一定程度上通用。

记得我在《ODCC随笔:整机柜资源池化需要高可用吗?》一文中曾经这样写道:“国内的情况有些特殊,BAT主要还是从OEM采购服务器,但成本却压得厉害… 不知有没有人觉得OEM赔钱的状况还会多久?总之我不认为这是良性的…”

今天我要写的内容,就是围绕这款微软的“Project Olympus”参考平台展开。

OCP非集中散热设计、Remote Heatsink特点

我认为Project Olympus在结构和散热方面的最大特色,就是针对高功耗CPU可选“Remote Heatsink”(这里实在是不太好翻译)。从图中不难看出,是若干热管从CPU上方引出到一个长条的散热排,以增大散热面积。

写到这里不得不从整个系统的角度来考虑。主板、扩展卡和I/O接口都在机箱前端,6个N+2冗余配置的风扇在最后端,这种设计有点位于传统机架服务器与OCP/天蝎整机架之间的感觉?其散热方案应该比之前灵活,因为不依赖统一的风扇墙,节点数量可多可少。

但由于风扇应该是从内部抽风,而且距机箱中部的CPU距离较远,难以形成较大的风压,所以才想到“Remote Heatsink”这个加强方案吧。

图中余下的还有8个M.2 NVMe SSD、50G网卡等,而“Next Gen CPUs”引起了我的注意。

在《初探OpenPOWER9服务器设计:x86不再寂寞》一文中,我提到过POWER9处理器在一些规格及功能创新上,已经超出了现在和下一代Xeon。那么在Xeon E5 v5正式推出之前,能通过公开信息也多了解一些也是不错的。

96lane PCIe、12 x SATA直指下一代Purley平台

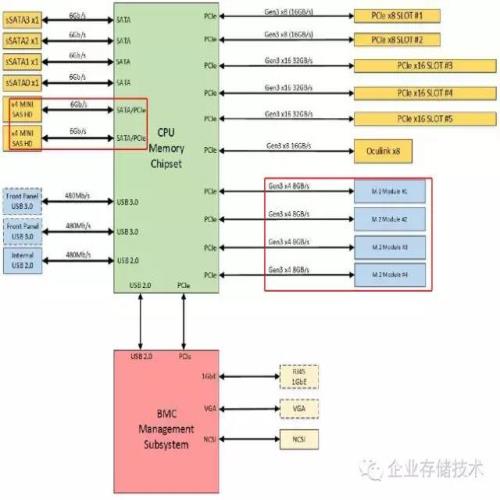

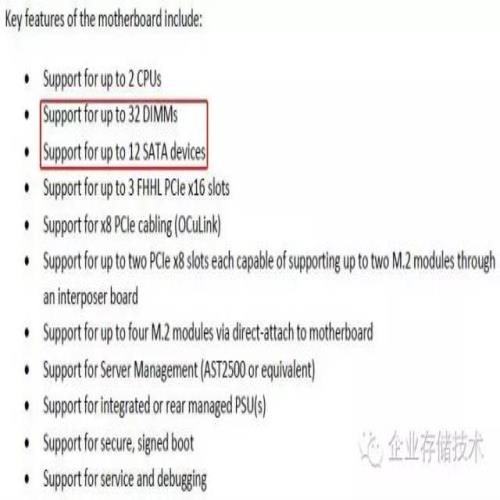

估计是由于Intel的NDA,微软和OCP也不方便写的太清楚,架构图中CPU、内存和芯片组放在了一个逻辑块里。不过还是能看出一些迹象,比如右边的PCIe Gen3 lane数量总计已经达到了88个,如果再加上左边2个x4 miniSAS HD引出的8个总共就达到96 lane PCIe。当前Xeon E5-2600每CPU提供40个PCIe Gen3 lane,加上PCH南桥那8个Gen2的也达不到。

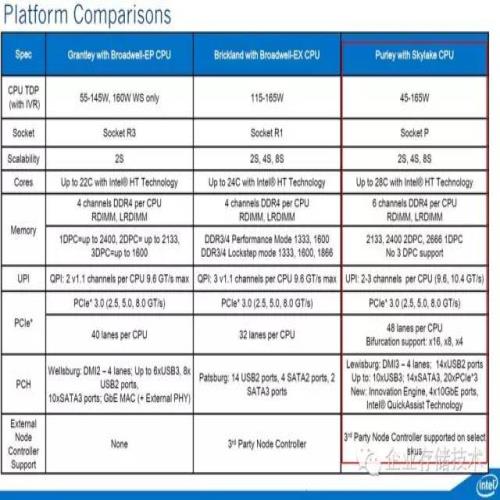

正如我们之前曾经列出过的下图,Intel下一代Purley平台(应该是Xeon E5 v5吧?)每CPU的PCIe Gen3 lane数量将达到48个。

另外那2个x4 miniSAS HD看上去是通用设计,除了PCIe之外还支持(可选)SATA 6Gb/s信号,这样PCH直接提供的SATA接口就可达到12个,也不是Xeon E5v4平台能做到的。

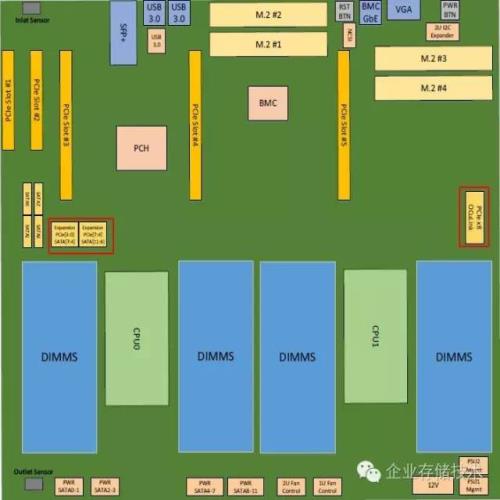

可能有朋友会问:要那么多PCIe有什么好处?其实上图中已经标出有4个Gen3 x4的M.2 SSD接口了,此外还有一个Oculinkx8在这里是什么用途呢?

我们看到,下一代Lewisburg PCH芯片组将提供14个SATA3,以及20个PCIe 3,只是受限于与CPU之间4 lane DMI3接口的限制,这些PCIe的性能不会太好。

在4通道内存控制器的前提下,双Xeon E5平台最多设计24根内存插槽(每通道最多3条)。上面写Skylake CPU将支持6通道内存,但没有3 DPC,按这个来看最多应该还是24条内存?

而在Project Olympus主板规格中,写的却是最大32个DIMM?看来最终产品与当初的Roadmap可能会有变化。

M.2+U.2——NVMe SSD大行其道

在双路服务器主板上出现4个M.2 SSD位置,您想拿它干什么用?

同时,我也还红框标出了miniSAS HD(PCIe或SATA信号)和Oculink x8的位置。PCIe信号的miniSAS HD接口能做什么?显然是连接到U.2(SFF-8639)SSD或者背板。在当前的服务器上一般还需要下面这种卡做个转接。

上图引用自《服务器设计进化:戴尔R930跨代对比之存储篇》一文,在四路服务器PowerEdgeR930上可选配2块这样的PCIe扩展卡,来支持一种存储配置——前端热插拔8 x NVMe SSD+16 x SAS/SATA。

FPGA支持:PCIe/Oculink、未提整合进CPU

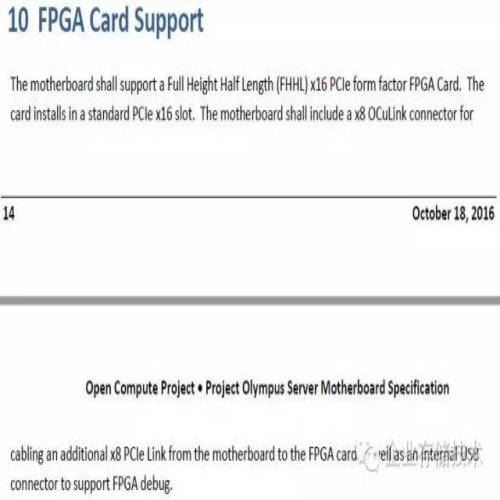

最后,我还在文档中看到了FPGA。微软提到了2种用法:一个是全高半长的x16 PCIe标准插卡;还有就是用Oculink线缆从主板连接到FPGA卡,同时一个内部USB连接器支持FPGA调试。

在ODCC峰会上,我看到一款百度的服务器上已经提供了4个Oculink,当然它应该也是支持NVMe SSD的。

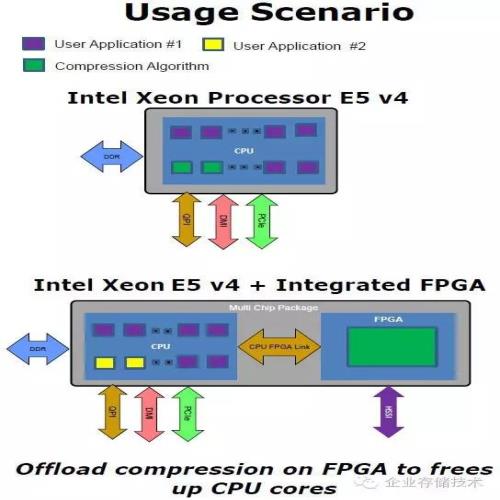

而根据我从今年秋季IDF了解到的信息,Intel从Xeon E5 v4就会开始提供一种多芯片封装——即CPU和FPGA两个Die封装在一颗处理器上。这么看微软Project Olympus平台上还是传统的用法。

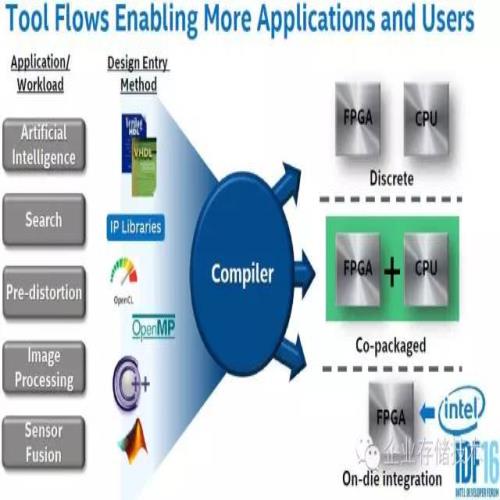

从这个图来看,Intel最终应该是要将CPU和FPGA做On-die的整合,从现在看还有些遥远了吧。

互联网是参考,但不是全部

如果Intel本次不跳票的话,我感觉Purley即下一代Xeon平台应该会在明年出来?特别是在遇到POWER9的压力之后。

不过说到底,微软这个“半成品”只能做个参考,因为互联网与传统企业级应用的需求不同,前者更加在意成本,迭代快,也会率先尝试有些技术的应用(比如资源池化),而通用服务器则会考虑用一款机型覆盖尽可能多的用户需求,由于生命周期较长,产品往往也要更加稳健成熟一些。

那么,就让我们一同恭候PowerEdge 14G、ProLiant Gen10(按照之前命名规律推断,请大家以官方信息为准)等新一代服务器的到来,届时我希望还能为大家点评一二:)

相关阅读:

《IDF随笔:RSA|天蝎存储池化的理想与现实》

《一项Xeon E5-2600 v4测试数据的背后》

注:本文只代表作者个人观点,与任何组织机构无关,如有错误和不足之处欢迎在留言中批评指正。进一步交流技术,可以加我的QQ/微信:490834312。如果您想在这个公众号上分享自己的技术干货,也欢迎联系我:)

尊重知识,转载时请保留全文。感谢您的阅读和支持!《企业存储技术》微信公众号:huangliang_storage

原文链接:http://mp.weixin.qq.com/s?__biz=MzAwODExNjI3NA==&mid=2649774972&idx=1&sn=8c4f2f93c3a22d623b70d168e8f837c7&chksm=83773a21b400b337cfe341c0bb8ca501d26d75edf4614f0bccad7f3b39a210754e9b1c2fee16#rd