本文内容非商业用途可无需授权转载,请务必注明作者、微博ID:唐僧_huangliang,以便更好地与读者互动。

今天看到新闻,AMD在国内外开始公开宣传Zen架构的服务器CPU——代号Naples(那不勒斯),规格上甚至有秒杀Intel Xeon E5 v4乃至下一代Skylake的感觉。

为了服务器,Intel必保桌面市场?

上周末有点想写东西,因为看到AMD Zen桌面CPU推出之后,有人纷纷讨论Intel不能再“挤牙膏”了。而在不久之前,Intel还曾提出要减少对桌面处理器的投入,全力发展数据中心产品线。

然而,在衡量这两块业务时不能只看净利润,也要看出货量和销售额。毕竟Intel优势的制造工艺和产能是那么多Fab晶圆厂在背后支撑。如果没有桌面处理器的数量,如何能维持庞大的制造体系和半导体研发投入。

除此之外我还有另一个观点:如果Intel在桌面市场让AMD Zen取得较大的占有率,积累的利润和经验估计会投入更赚钱的领域——服务器CPU,到那时Intel将会面临比较被动的局面。反过来说,Intel也意识到应该精简桌面CPU型号和系列,还有关键一点就是不要太限制核心数量——针对单路服务器/工作站的Xeon E5-1600系列已经达到8核,而主流Xeon更是在20核以上,这方面完全不是技术限制。

记得昨天在一个群里我还说现在不关注AMD CPU了,没想到今天又不得不写这方面的东西,因为涉及到企业级市场的技术。

单路128 lane PCIe、双路一共为何还是128?

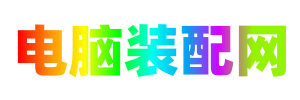

还是国外网站上的ppt图更加原汁原味一些。AMD Naples号称System on a Chip,应该不是连B350/PCH这样的南桥都不需要了吧?按道理有些低速功能模块与CPU分开才好一些吧,除了像Atom、Xeon D这些要求高集成度的“嵌入式”领域。

相关阅读:《让Cisco背锅的Atom - 时钟IC和晶振那点事》

由于AMD新一代服务器CPU的规格早提前泄露出来,当初在我听到整合128 lane PCIe、8通道内存控制器时,一直在想对应的CPU插座引脚数量会达到什么规模?要知道,下图中的XeonPhi 7200(x200)系列的LGA-3647(Socket P)处理器,已经比现在的LGA-2011增加了一千多个触点。下一代的Xeon E5 v5(代号Skylake)应该也是用LGA-3647,那么AMD Naples会不会比这个还要大?

Intel Xeon Phi 72XX Processor背面照片,更多详情参见《Xeon Phi x200要自我互连,CPU靠边站》

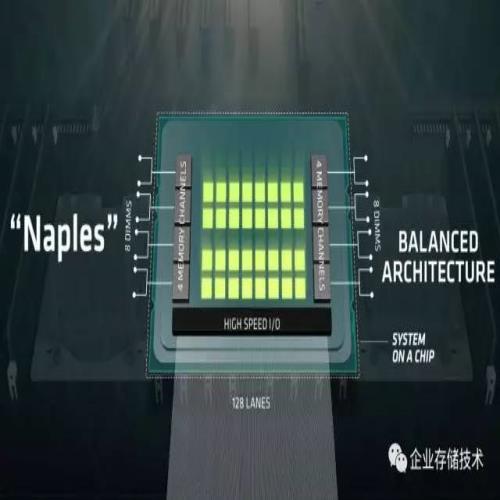

再看这张图,是不是有点豁然开朗的感觉?在双CPU工作模式下,每颗AMD Naples的PCIe lane数下降为64,也就是将一部分高速I/O资源重定义为CPU之间的FABRIC互连通道了。这种高速接口复用同一套物理层的情况在别的产品上也有出现,比如Power 9的PCIe和NV-LINK接口、Intel PCH南桥的PCIe/SATA/USB 3.0,还有兼容FC/以太网的多协议网卡、交换机等。

关于SMT同步多线程已经不是新闻了,从Zen这一代开始,AMD终于能够直面Intel Hyper-Treading了。

看AMD的幻灯片(paper)功夫

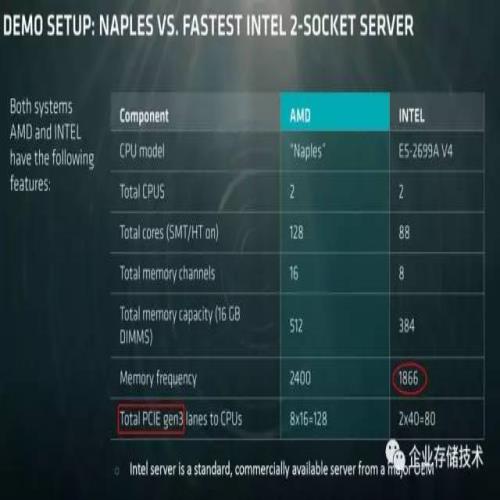

上面这张ppt,AMD有些田忌赛马的味道了。首先Intel Skylake已经量产并供货给国内外大型互联网用户,而Naples还未正式发布(据说下半年量产)。

同时参考下面一张图:

AMD拿32核跟Intel 22核比,而Intel到了Skylake最多28核;

AMD Naples每CPU 8个内存通道,Intel目前4个,Skylake是6个;

Intel由于每通道能插3条内存,所以容量上小扳回一程(而这正是AMD接下来挖的一个坑);

DDR4内存频率,Intel现在明明支持2400MT/s,而AMD按照你插满3条时的1866MT/s来对比,另外Skylake据称没有3DC(3 DIMM per Channel)支持;

PCIe都是3.0,AMD是拆成每CPU 4个x16来计算,Intel XeonE5一直是40个PCIe lane,Skylake增加到48个。

虽然我们看AMD有点不厚道,但规格至少是做上去了。而且美国广告法有一点,处于劣势的厂商在公开宣传时对比尺度可以相对大一点,所以从20年前 AMD开始这么干Intel也无法效仿。相比之下,国内某司的营销尺度,在他们自称市场份额领先之后似乎也没啥明显改善,谁让咱们这里那啥不健全呢:)

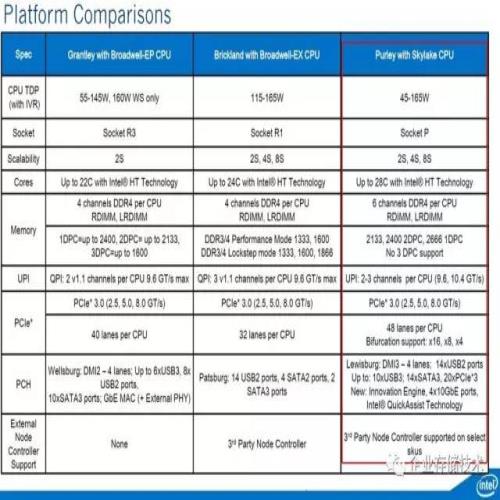

上图我在《下一代Xeon E5服务器抢先看:NVMe、FPGA爆发》一文中曾经引用过。请大家注意一点,从Skylake和Purley平台开始Intel QPI改称UPI(除了CPU还能连别的,比如FPGA?),同时速率上升到10.4GT/s,后面我就要对比这个。

3通道UPI估计是对应下一代XeonE7,E5应该还是2通道。另外,最下面一条——第三方Node Controller就是我在《Bull 8-16路服务器:为何基于双CPU模块互连?》中提到的多处理器互连专用芯片。

AMD Coherent Fabric真比Intel QPI/UPI快那么多?

上表引用自一个国外网站http://wccftech.com/amd-naples-32-core-zen,不知是否故意在标明100GB/s AMD Coherent Fabric一致性互连时,没有写出它与PCIeI/O之间的共用关系,也没有对应写出Intel的QPI。

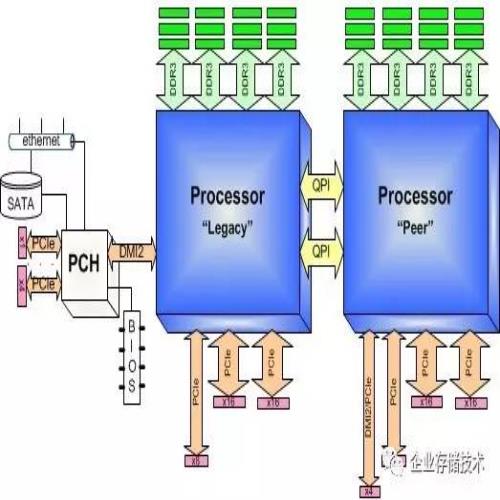

上图引用自较早的第一代Intel E5-2600文档,仅用于体现QPI连接。如今DDR3内存升级到DDR4,PCH南桥也有变化,PCIe控制器倒还是Gen3 40lane。

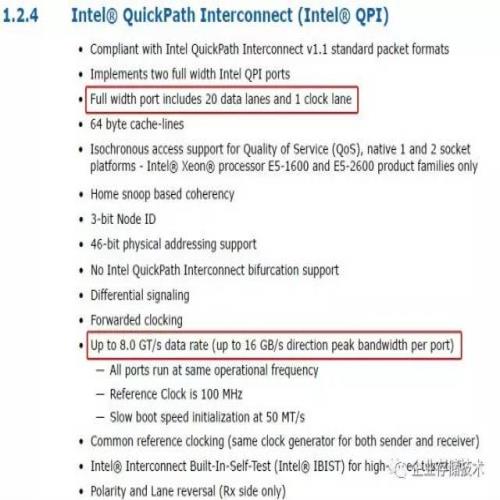

上面这段来自同一份文档,按照当时的QPI 8.0GT/s来计算,20 data lane宽端口物理数据传输率应该达到160Gbit/s,Intel这里写的16GB/s单向最大带宽估计是用了8b/10b编码。

记得Intel在QPI应用初期6.4GT/s的时候,还宣传过25.6GB/s的带宽(全双工),这是因为每个lane都是双向的。那么对应到9.6GT/s和10.8GT/s的QPI就是38.4GB/s、43.2GB/s带宽。Skylake的2条UPI双向带宽之和可达86.4GB/s。

从这么看AMD的100GB/s优势就不是特别大了。如果按64个8GT/s PCIe 3.0来计算,双向带宽按道理还不只这个数值,估计定义为CPU间互连时还是保守一些。

内存带宽:理论与实际

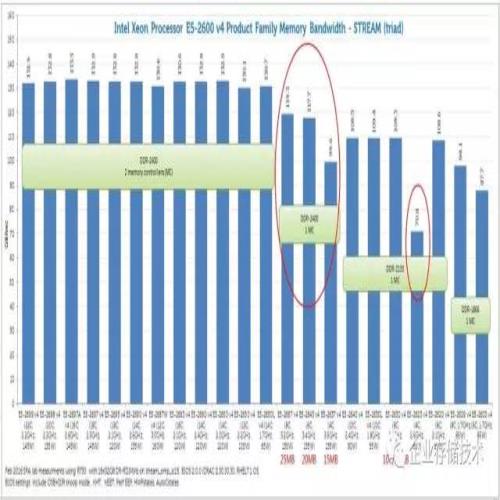

上图为Intel Xeon E5 v4四通道内存控制器的最大带宽,NUMA架构下2颗CPU如果同时访问本地内存总带宽可以达到x2(153.6GB/s)。相比之下,AMD一颗Naples理论上就能达到同样的效果(2颗是不是超过300GB/s了,我看国内新闻写“170G/s的单内存插槽”不知咋算的)。

至于Intel Skylake的6通道DDR4-2666,计算出来是每颗CPU 127.68GB/s,比Naples应该是落后一些。

这个图表引用自《一项Xeon E5-2600v4测试数据的背后》一文,在STREAM测试中,刚才说153.6GB/s的双路Xeon E5 v4系统实测内存带宽超过130GB/s。因此,我更想看到AMD Naples实际测试的性能数值是多少。

AMD Naples只支持双路:先把这个做好再说

我们知道Intel Xeon E5还有一种拓扑方式:

Xeon E5-4600四路平台CPU、内存连接示意图,它与XeonE7之间的差别我就不重复了。

Xeon E5四路平台与E7相比除了有性价比优势之外,还容易实现更高的密度,因为每个CPU不用搭配4颗SMI-2内存缓冲芯片(如DellPowerEdge R930的内存板)。所以我们看到R830可以做到2U高度。

举个例子,在PowerEdge M830四路刀片(XeonE5-4600)的基础上,Dell还衍生出用于FX2模块化平台的FC830服务器节点,在2U机箱中可以实现2台四路,或者1个FC830加上2个FD332存储模块(支持2x 16个2.5英寸热插拔硬盘/SSD)。

关于PowerEdge FX2上的FD332结构和PCIe连接,我在《数据中心选址贵阳理由:天、地、电》一文中曾有过实物介绍。

对于AMD Naples目前只支持单路和双路服务器,我觉得是个合理的选择,在这个市场打开之前,你能做四路恐怕也没多少人敢用。AMD服务器CPU在我记忆中还停留在LGA 1207、HT 3.0的时代,企业级市场更看重稳定,Intel这么多年的积累不是白给的。按照AMD公布的规格,Naples的封装和pin脚可能比LGA-3647还要大,能否按时出货、其市场需要多长时间成熟起来还是一个问号。

x86软件兼容性:令OpenPOWER垂涎三尺

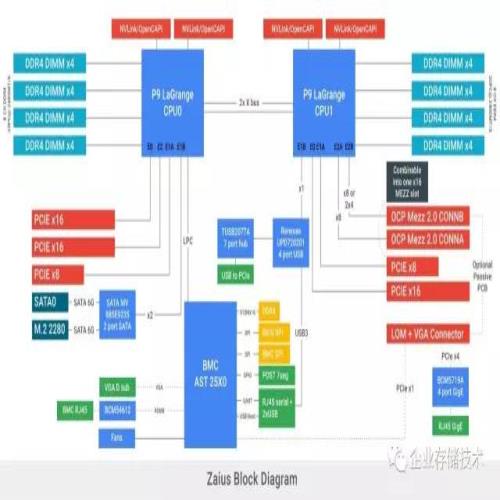

上图曾在《初探OpenPOWER9服务器设计:x86不再寂寞》中列出过。其实我挺喜欢Power9的,估计将是第一个支持PCIe 4.0的服务器平台吧,还有NV-Link和OpenCAPI,可惜指令集——软件生态是它发展的一个障碍。

总之,我觉得看到AMD Naples给Intel带来挑战不是一个坏事情:)

注:本文只代表作者个人观点,与任何组织机构无关,如有错误和不足之处欢迎在留言中批评指正。进一步交流技术,可以加我的QQ/微信:490834312。如果您想在这个公众号上分享自己的技术干货,也欢迎联系我:)

尊重知识,转载时请保留全文。感谢您的阅读和支持!《企业存储技术》微信公众号:huangliang_storage

原文链接:https://mp.weixin.qq.com/s?__biz=MzAwODExNjI3NA==&mid=2649775569&idx=1&sn=c5ebcd2eedfdfecfefedf64714ba6e47&chksm=83773c8cb400b59ab80f618cb9f7398ba1ec2dd4f31ba3dcb5be2938ba151fcede40b41b2448#rd